昆明舞台桁架搭建厂家分析为什么市面上的铝合金舞台桁架更受欢迎?对此,昆明舞台桁架搭建厂家介绍道,铝合金舞台桁架搭建的舞台造型宏伟大气,视觉冲击力强,展会特装搭建、广告公司、展览公司,婚庆公司等的优[详情]

电梯维修实训装置哪家靠谱?昆明电梯维修实训装置生产厂家,会深入研究电梯维修行业需求,装置模拟真实电梯故障类型,涵盖机械维修与电气调试等多个实训模块。我们作为本地专业昆明电梯维修实训装置生产厂家,产品采用标准化设计

休闲山庄哪家靠谱?先查真实评价,优先选开业 10 年以上的老店,如一丘田金殿瓜果庄园,本地口碑稳定,收费透明(烧烤桌费、食材价目公开);再看资质配套,青竹村山庄有正规营业执照,停车场免费且容量大,不会出现 “停车收费” 等隐性支出;

下面福州废旧品回收厂家来和大家分享一下介废旧品回收要注意什么? 废旧品回收的管理要注意什么?回收单位应每年至少一次定期进行废旧物资的库存盘点,做到账账、账实相符,并将盘存情况报送主管税务机关。注意配合主管税务机关科学测算、约定废旧物资耗用率。

SMT(表面贴装技术)是一种广泛应用于电子组装的技术,虽然它具有节省空间等优点,但在实际生产过程中,仍然会遇到一些常见的问题。以下是一些SMT贴片过程中常见的问题及其简要分析:

汽车连接器是苏州线束厂家经常接触到的一部分。其功能简单:在电路被阻挡或独立电路之间建立沟通桥梁,使电流流通,使电路实现预定功能。汽车连接器的方式和结构是不断变化的,一般由四个基本结构部件组成,即:外壳(根据类型)、接触部件、附件、绝缘材料。

球墨铸铁沟盖板是一种用于城市基础设施的重要组件,广泛应用于市政工程、道路建设和排水系统等领域。其主要功能不仅是覆盖和保护下方的沟渠、管道,还具有防沉和防盗的特性,确保城市运行

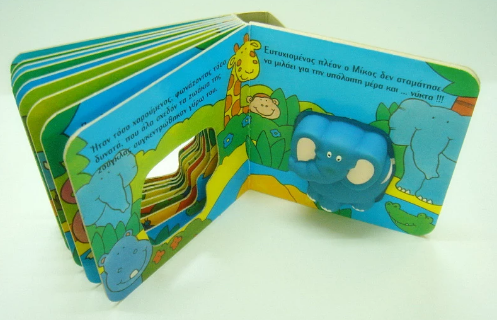

当前,一些公司为了提高宣传效果,经常会设计印刷杂志。由于公司缺少专业设计人才,制作公司在设计杂志时通常会联系专业的印刷公司完成。那么,印刷公司印刷杂志并不是难事,通常要把握以下几个重点?

市场上流通的手提水果包装纸箱来看,主要可以分为三种形式:自带提手型、塑料提手型和绳提式型。有三层纸箱、五层纸箱。水果纸箱制作常用300g或350g的灰板纸/白卡纸裱瓦楞纸,纸箱材质的选择决定着沉重、抗压等性能,通常情况下水果包装纸箱提手一般多高?

福州车牌识别系统(License Plate Recognition, LPR)作为智能交通管理的重要组成部分,其规范安装要求对于系统的性能和稳定性至关重要。以下是车牌识别系统的规范安装要求:

重型仓储货架安全使用规则帮助大家正确并安全的使用,很多货架事故就是因为没有遵守安全使用规则下面来详细的看一下。

防雷检测是指为确保建筑物及其周边环境在雷电天气下的安全,对防雷设施和系统进行检查、测试和评估的过程。这项工作在现代社会中变得越来越重要,主要原因可以归纳为以下几点:

西安代办建筑资质延期,无疑是一项考验专业度与细致度的任务。其中所涉及的注意事项繁多而细,如同织就一张密不透风的网,每个环节都需如履薄冰般小心翼翼,以保整个代办流程的顺利无阻。

如何包装袋批发价是否合理?合理批发价应包含基础增值服务(如免费设计、送货上门),若厂家报价低但额外收取设计费、运费(如昆明到玉溪的运费另算),实际成本可能更高;质优厂家会将基础服务纳入批发价,提升性价比。

实验室装修设计是一个复杂且细致的过程,涉及多个学科的知识和技术,尤其是在对所使用材料和产品的选择上,更需严格把控,以确保实验室功能的有效性与安全性。以下是对实验室装修设计中使用产品的主要要求。

不同的主题设计所配套的标识牌也是不一样的。不同主题的标识牌,吸引着全国各地的往来游客,也通过标识牌的主题细节展示,体现了不同酒店的高贵品质。那么,在设计酒店标识牌时,需要考虑哪些方面呢,今天,我们中涵标识就带大家一起来看看。

呼吸机儿童款与成人款有什么不同?瑞思迈儿童款呼吸机体积更小、重量更轻,方便放置在儿童卧室,机身颜色与外观更贴合儿童喜好,减少孩子对设备的抵触;面罩采用柔软硅胶材质,尺寸根据儿童面部发育特点设计,避免压迫面部影响骨骼发育;设备压力调节范围更窄,符合儿童呼吸道压力需求,

2026.5.20封边工序的本质,是通过封边胶将板材端面与封边条牢固粘结,形成密闭、美观、耐久的边缘结构。粘结是否牢固、是否耐温耐潮、是否长期不开胶,关键取决于界面粘结质量,而界面粘结的核心在于胶体与基材之间的润湿、嵌合与分子结合。

清污机厂家如何选?有水质适配方案的,能避免设备 “一刀切” 导致的问题。建议与厂家详细沟通水域水质参数,让方案更准,确保清污机高效运行。提供带前置沉沙装置的清污机,先沉淀部分泥沙再进行过滤,减少滤网磨损与堵塞;同时采用耐磨材质刮板(如高锰钢刮板),延长部件使用寿命

提到工业表面处理,许多人的印象或许还停留在粉尘飞扬、气味刺鼻的传统作坊场景。然而,随着智能制造与环保理念的深度渗透,现代化的特氟龙(PTFE)喷涂车间早已发生了翻天覆地的变化。今天,就让我们一同走进标杆企业的实地工厂,揭开这层“工业防护外衣”背后的创新面纱,看看传统喷涂工艺是如何通过技术迭代实现华丽转身的。

空调以旧换新比线上更划算吗?除旧机抵扣外,专卖店还可叠加云南本地补贴(如家电下乡补贴、专卖店专属优惠券),以海信热门型号 KFR-35GW/E500-A1 为例,线上以旧换新后约 2399 元,专卖店叠加补贴后仅 2199 元,更划算。

新疆是产棉大省,在此基础上,孕育了较多的化纤绵生产企业与厂家,喷胶棉作为化纤绵行业中重要的产品之一,在新疆喷胶棉生产厂家的各类产品中,都有什么优缺点,厂家销售的都是什么样的喷胶棉呢?

看懂西装面料才能避免踩坑 有多少人在定制西装时踩过坑的麻烦举个爪?都说每个行业的水都很深,对新手来说几乎很难避免踩坑的问题

西洋参颗粒加工成固体饮料是一个结合了传统药材与现代食品加工技术的过程。增强免疫力:西洋参中的人参皂苷成分能够有效增强机体免疫力,提高身体抵抗力。 抗疲劳:西洋参具有抗疲劳的作用,可以减轻身体疲劳感,提高运动耐力。 改善认知功能:西洋参可以促进大脑功能的作用,改善记忆力和注意力,有助于提高学习效率和工作效率。 辅助治疗慢性疾病:西洋参还可以辅助治疗一些慢性疾病,如糖尿病、高血压等,有助于调节血糖和血脂水平。